Intel CPU Roadmap with Sapphire Rapids structure completely different from ASCII.jp Ice lake

Let's continue to tell you the details of Intel's new product. This time it's about Sapphire Rapids. So, in Intel Architecture Day and HotChips, the content is "almost" the same. The only difference is the topics around SVM and S-IOV described later. Therefore, I mainly want to explain while using Architecture Day slides.

Sapphire Rapids that improves performance through multi-chip

Sapphire Rapids is designed to improve node performance and data center performance. Specifically, to improve the IPC, the node performance strengthens the peripheral circuit to support this, by introducing a mechanism to help expand / scale the construction of the server, in an attempt to improve the effective performance of the entire system, which is the data center performance.

Node performance, new core mass cache and high-speed memory, and the increase in the number of cores itself is an indisputable methodology.

In fact, there is not much detail about the data center performance. In particular, the interrupt virtualization between QoS and processors may give details when the product appears in the future.

Although it is an implementation method, it provides a multi-chip (Multi Tile in Intel parlance) structure, as explained in the 629th serial.

Sapphire Rapids improves performance by making multi-chips. This slide also appears on Architecture Day.

さすがにインテルとしても、Xeon向けに巨大なダイを作り続けるというのはそろそろ限界に達したらしい。もっと正確に言えば、巨大なモノシリックダイの限界値はおおむね700mm2かそこらになる。これはどういう話かといえば、半導体製造におけるステッパーによる露光のフェーズで、マスクサイズの限界というものが存在するからで、これがおおむね600~700mm2(これは利用するプロセスやステッパーの性能に依存する)になる。

わかりやすい例が連載572回で紹介したCelebras SystemのWSEである。ダイそのものは4万6225mm2となっているが、写真を見ていただくとわかるように内部はこれを12×7で84個のタイルに分割しており、タイルあたりの面積は550.3mm2かそこらになる。

Cerebras SystemsのWSE。ダイサイズ4万6255mm2や1.2兆トランジスタ、40万コアなど、いろいろ数字がインフレし過ぎている

As explained on page 3 of 572 serial series, the chip is made by separating 84 tiles at a time and then reconnecting them in the way of wiring. In this sense, it cannot be said to be a single chip.

今回このSapphire Rapidsのタイルの面積は400mm2前後とされており、つまり4つでは1600mm2に達する。これをモノリシックで作る方法は現実問題として存在しない。したがって、よりコア数やキャッシュ、搭載するアクセラレーターなどを増やしたり、コアそのものを強化する(=コアのエリアサイズが増える)場合、マルチタイル方式は必須というか避けられない選択肢だったと言える。

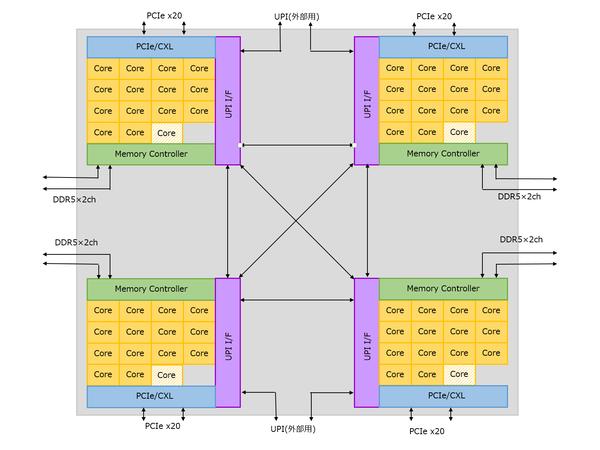

As the following image shows, the structure is four identical tiles, core and LLC, memory controller, UPI,PCIe/CXL, accelerator placed on each tile, Link (I think this is based on UPI Intel did not elaborate on this way), this is a way to connect.

Configuration of Sapphire Rapids. In this case, there are physically four kinds of chips, of course, this is a pattern diagram, which does not mean that the actual chip is configured like this.

In short, its structure is the same as that of AMD's first-generation EPYC. AMD switched to a way of separating the core from Imax O in the second generation of EPYC, but Intel is a little interested in what direction it will take in the future.

So, as far as the core of Sapphire Rapids is concerned, it is the same as the P-Core of Alder Lake described last time. However, as explained at the end of the last time, facing Sapphire Rapids has the following differences:

In addition, there are slight differences. Among them, AMX has been explained in 629 serial times, so it is omitted. With regard to AVX512, the specification of AVX512-FP16 was released in June this year as a basis for installation.

After that, AiA explained that it was the story of the new accelerator-oriented Iripple F. However, it is not clear whether this is just an internal device or whether external accelerators are also supported through CXL. I always feel that I also support CXL.

All in all, in the existing AVX512, if it is FP32, it can do up to 16 operations / cycles, while if it is AVX5412-FP16, it can do 32 operations / cycles. For 16-bit operations, BF16 support has been added for Cooper Lake, but it is the first for FP16,Sapphire Rapids.

The CLDEMOTE command is actually originally implemented in Tremont, and it should be said that the author forgot this at first. The CLDEMOTE command, officially known as the "Cache Line Demote" command, should move the Cache Line containing the address specified by the Operand to the cache closer to the processor core (that is, the primary data cache or the secondary cache). And processor "Hint To" commands.

It is not immediately excluded from the 1 or 2 caches, but the next time the processor replaces the data cache and 2 caches, indicates to the processor that the area of the cache should be swapped out 2 / 3 times first.

This is particularly effective in communication between processors. P-Core/E-Core implements level 2 / level 3 caching in the form of Exclusive Cache (exclusive cache). Therefore, after a core overwrites memory (which is only saved in a cache at this time), if its address is written back to the level 3 cache with the CLDEMOTE command, other cores can quickly refer to its contents.

This CLDEMOTE command may also be installed in E-Core, but according to the instructions, the CLDEMOTE command is invalidated in Alder Lake, so only Sapphire Rapids is currently available.

![lifehacker lifehacker LifeHacker LifeHacker A carabiner that is convenient for cutting packaging at the entrance. Excellent sharpness for medical blades! [Today's life hack tool] lifehacker lifehacker LifeHacker LifeHacker A carabiner that is convenient for cutting packaging at the entrance. Excellent sharpness for medical blades! [Today's life hack tool]](http://website-google-hk.oss-cn-hongkong.aliyuncs.com/drawing/223/2022-3-2/28016.jpeg)

![lifehacker lifehacker LifeHacker LifeHacker [2021] 7 Recommended Dishwashers | Introducing High Cospa & Compact Products lifehacker lifehacker LifeHacker LifeHacker [2021] 7 Recommended Dishwashers | Introducing High Cospa & Compact Products](http://website-google-hk.oss-cn-hongkong.aliyuncs.com/drawing/223/2022-3-2/30293.jpeg)

Masaki Aiba's "VS Damashii" member theme song project started!Shori Sato & Yuta Kishi laugh at orders in English

We take the place of ... Children who directly appealed to His Majesty the Emperor for the release of his father in the Nara period (December 11, 2021) --Excite News

The 26-year-old who doesn't know love met ... "Literature Virgin-The Story of Late Blooming Love-" (November 22, 2021) --Excite News

How can I create music with Deep Learning? -Builders.flash ☆ -Builders.